현재 반반택시 어플을 다운받으시고 초대코드를 입력하시면 8000원의 혜택을 받으실 수 있습니다!

(회원가입 5000원 + 초대코드 3000원)

어플 내에서 4가지 기능을 사용할 수 있습니다. 또한 반반택시란 동승자를 임의로 배정해줘서 택시비를 줄여주기 때문에 장거리 뿐만 아니라 택시를 자주 타시는 분에게 유용한 어플이 될 것 같습니다.

또한 반반택시는 다양한 장점을 가지고 있습니다.

그 외에도 일반호출도 가능 하므로 적립금 받아 가셔서 회원가입하시고 초대코드 입력하셔서 8000원 할인 받으세요!!

아래에 있는 초대코드를 입력시 추가 포인트를 받아가실수 있습니다!!!

- 반반택시 초대코드 , 추천인 적립 코드 : CV3UR2

- 포인트 받는 법 : 반반택시 가입 후, 초대코드 입력하기 메뉴에 초대코드를 입력해주세요.

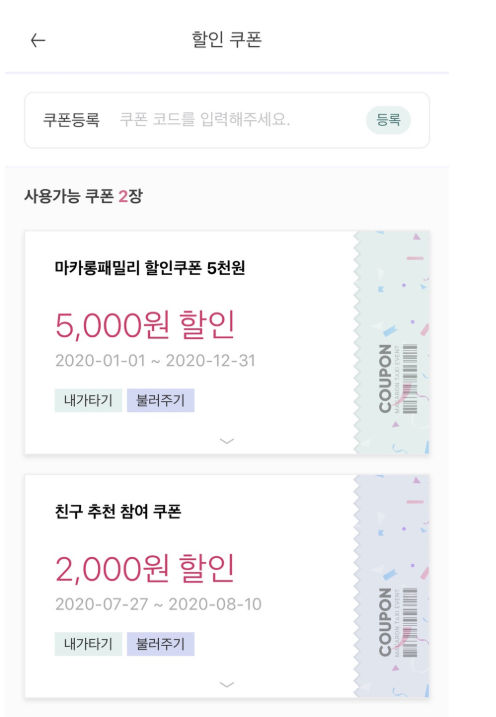

- 혜택 : 회원가입 5,000P / 초대코드 입력시 3,000P

- 신규가입자에 한하여 초대코드 입력이 가능합니다.

'여러가지' 카테고리의 다른 글

| 마카롱택시 타고 7000원 할인받자 (추천코드 : Q0KCW4) (0) | 2020.07.29 |

|---|---|

| 산업용 PC란 ? ( 소비자용 PC와의 차이 ) (0) | 2020.07.21 |